(Sorry, Text in french only)IntroductionDepuis plus de 20 ans, les BUS entre le CPU et ses cartes périphériques sont conçus de la męme façon. Une grande série de fils disposés parallčlement entre les broches du CPU et celles des cartes périphériques. Plusieurs se souviendront par exemple des BUS S100, ISA, AT et VME. Mais nous connaissons les BUS encore populaires comme les PCI, PCI-X ou AGP qui sont toujours conçus selon ce męme principe. Des défis de taille attendent les développeurs de circuits BUS ainsi que du PCB qui en résulte.

Limites de développementCette façon de concevoir atteint ses limites avec l’arrivée des nouvelles technologies. Les nouveaux CPU qui traitent des mots de 16, 32 et męme 64 « bits » augmentent d’autant le nombre de fils ŕ interconnecter. Pensons ŕ la vitesse des signaux qui transitent par le BUS. Avec ces nouveautés, le nombre de couches du PCB augmentent, l’adaptation des interconnexions est plus que jamais délicate ŕ réaliser et sans oublier le rayonnement radio associé aux traces du PCB qui augmente significativement. Ces critčres, loin de simplifier la réalisation de circuits, augmentent de façon importante les défis technologiques qui attendent tout ceux ŕ qui revient la tâche de concevoir le circuit final.Le temps de développement qui s’allonge, les coűts de fabrication qui augmentent, voici deux conséquences directes de ces réalités de développement. La compétitivité des entreprises manufacturičres est donc directement concernée. |

||

|

Recherche de solutionsL’industrie n’est pas indifférente ŕ cette réalité. C’est alors que quelques futés ont émis quelques hypothčses de solutions et se sont posé quelques questions de base. Pourrait-on s’inspirer des périphériques Ethernet, 1394 ou USB qui se connectent et se déconnectent ŕ notre guise? Pourrait-on diminuer le nombre de fils entre le CPU et ses périphériques? Comment réaliser un BUS série équivalent ŕ un BUS PCI opérant ŕ 33 Mhz? Quelle technologie permet une bande passante de 133 M Octets/sec sur une broche, ou de 533 MOctets/sec pour un BUS PCI-X. |

|

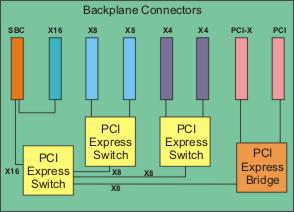

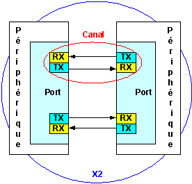

| Une lueur d’espoir est apparue. L’arrivée des circuits capables de sérialiser plusieurs signaux parallčles sur quelques fils, appelés canaux, révolutionne la conception des cartes mčres et des fonds de panier. Ces circuits de plus en plus populaires sont proposés par des compagnies majeures de l’industrie. Pensons seulement ŕ Intel, Altera, National Semiconductor ou Xilink. Baptisés «Switch » ces circuits remplacent les circuits « northern and southern bridge » que l’on retrouve sur la grande majorité des cartes mčres. | ||

|

Forte de l’apparition de ces circuits mais consciente de l’importance d’assurer la compatibilité entre toute ses « Switch », l’association américaine PCI/SIG s’est penchée sur le problčme. En guise de solution, le standard PCI Express a été proposé. Inspiré par le standard PCI, il respecte non seulement les paramčtres physiques de celui-ci, mais aussi les aspects logiciels comme les pilotes. La solution PCI Express se situe au niveau des circuits intégrés directement. L’architecture proposée est une interconnection de canaux (liens série ou Lane en anglais) entre les circuits (périphérique–périphérique, périphérique–CPU), entre les cartes électroniques ou entre les systčmes. | |

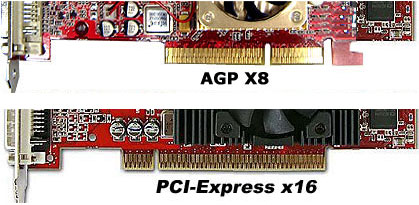

Augmentation de la vitesse des signauxLa vitesse des signaux constitue probablement le premier avantage du PCI Express. Un BUS PCI Express 16X, par exemple, a une capacité de transfert de 4 Giga Octets/sec et communique jusqu’ŕ 60 fois plus vite qu’un BUS PCI (33Mhz @ 32 bits). Étant plus performant qu’un BUS AGP, il est tout indiqué d’utiliser le BUS PCI Express, avec son BUS 16X, pour les cartes vidéo.

|

||

|

Possibilité d’ajustement de la vitesseL’ajustement de la vitesse aux besoins de son utilisation est assurément un autre avantage important. Le PCI Express permet une vitesse jusqu'ŕ 2.5 Giga Octets/sec par canal ajustable en six vitesses standards 32X, 16X, 8X , 4 X, 2X et 1X selon les besoins. Le PCI Express permettrait jusqu’ŕ 10 Giga Octets/sec par canal et l’utilisation de 32 canaux simultanément. Męme que le CPU comprendrait directement 2 canaux : 16X et 8X. On peut déjŕ envisager de nombreux avantages ŕ ce nouveau standard. Un concepteur peut maintenant implanter un canal haute vitesse 16X dédié au circuit graphique et un canal basse vitesse 1X dédié aux périphériques ŕ usage général. |

|

Diminution du nombre de canaux requisAutre avantage important du PCI Express est la simplicité d’interconnexion des composants. Le connecteur PCI Express de base n’a que 36 broches contre 120 broches pour le PCI. Il existe actuellement 4 variétés de connecteurs PCI Express, soient : X16, X8, X4 et X1. Différents uniquement par leur longueur, un connecteur X8 possčde tous les signaux de base du connecteur X1 et y addition 4 canaux supplémentaires. Le nombre de couches du PCB requise pour passer un canal se limite ŕ quatre. Conséquence directe, le coűt de fabrication du PCB est maintenu au plus bas. Les concepteurs auront la vie plus facile avec moins de fils ŕ considérer entre les circuits et moins de couches sur le PCB. Des économies substantielles sont envisageables au niveau de la fabrication des PCB ainsi que dans le temps de développement des circuits. |

|

|

Connexion ŕ chaud (Hot swap)Le PCI Express permet une déconnection ŕ chaud (Hot swap), cette caractéristique tant espérée pour la majorité des systčmes. Ouvrir le boîtier de son PC, dévisser le couvert, déconnecter les câbles, extraire le carte électronique pour y changer un composant par un composant identique peut ętre une expérience traumatisante. Elle le sera d’autant plus lorsque le systčme refuse de démarrer aprčs sa mise sous tension. Ŕ l’instar des nouveaux périphériques connectables et déconnectables ŕ chaud tels que les HDD Serial ATA, le PCI Express permet d’extraire une carte électronique de son connecteur męme si celle-ci est alimentée (ŕ chaud). Lorsque les circuits PCI Express sont conditionnés dans des boîtiers qui permettent une insertion ou une extraction simple, les coupures de service sont maintenues au minimum. On peut maintenant imaginer qu’en cas de panne, il est possible d’échanger le périphérique ŕ chaud trčs rapidement et ce peut-ętre męme sans que l’usager ne s’en rende compte. C’est en quelque sorte le « Carrier Grade system» abordable. |

||

|

Compatibilité avec le BUS PCIEnfin, un avantage indéniable du nouveau standard proposé est sa compatibilité avec les expertises existantes. En effet, l’organisme PCISIG a eu la bonne idée de conserver pour le nouveau standard le męme format que pour le PCI bien connu. Les dimensions physiques sont les similaires, la « braket » métallique est la męme. La compatibilité a été poussée jusqu’ŕ conserver le modčle informatique de programmation. Avantage d’importance, cette compatibilité permet aux concepteurs de logiciel de conserver leur code tel quel. C’est le chip qui fait tout le travail. |

|

Conclusion

Le BUS PCI Express apporte un nouveau souffle aux concepteurs de

circuits. Ce nouveau BUS performant permet de simplifier la conception

électronique, d’économiser sur le temps de développement, d’économiser

sur les coűts de fabrication des PCB, de réaliser des produits « hotswap »

facile d’entretien et de configuration. Les concepteurs ont déjŕ

accčs ŕ une panoplie d’outils de développement qui facilitent leur

travail et la mise au point de nouveaux produits. On retrouve entre

autres, des circuits d’évaluation, des systčmes de prototypages

et des analyseurs de BUS. Les études de marchés récentes démontrent

une popularité grandissante de ce nouveau standard auprčs des industries

de l'informatique et des communications. Le PCI Express succčde

aux architectures PCI et PCI-X actuelles. Les analystes prévoient

pour un avenir rapproché que les ordinateurs de type PC devraient

ętre basés majoritairement sur le standard PCI Express. |

||

Quelques liens complémentaires: http://www.expresslaneitnet.org/home http://developer.intel.com/technology/pciexpress/devnet/index.htm Quelques documents de référence: Complete PCI Express Reference : Design Implications For Hardware And Software Developers PCI Express System Architecture

|

||